概述

CH224单芯片集成USB PD等多种快充协议,支持PD3.0/2.0,BC1.2 等升压快充协议,CH221单芯片集成USB PD快充协议,支持PD3.0/2.0快充协议。CH224和CH221都支持自动检测VCONN及模拟E-Mark 芯片,最高支持100W 功率,内置PD通讯模块,集成度高,外围精简。集成输出电压检测功能,并且提供过温、过压保护等功能。可广泛应用于各类电子设备拓展高功率输入如无线充电器、电动牙刷、充电剃须刀、锂电池电动工具等各类应用场合。

功能特点

- 支持4V 至22V输入电压

- 支持PD3.0/2.0,BC1.2等快充协议

- 支持USB Type-C PD,支持正反插检测与自动切换

- 支持E-Mark 模拟,自动检测VCONN,支持100W 功率的PD请求

- 请求电压可通过多种方法动态调整

- 单芯片集成度高,外围精简,成本低

- 内置过压保护模块OVA、超温保护模块OTA

应用场合

- 无线充电器

- 笔记本电脑充电线

- 锂电池小家电

- 锂电池电动工具

- 移动电源

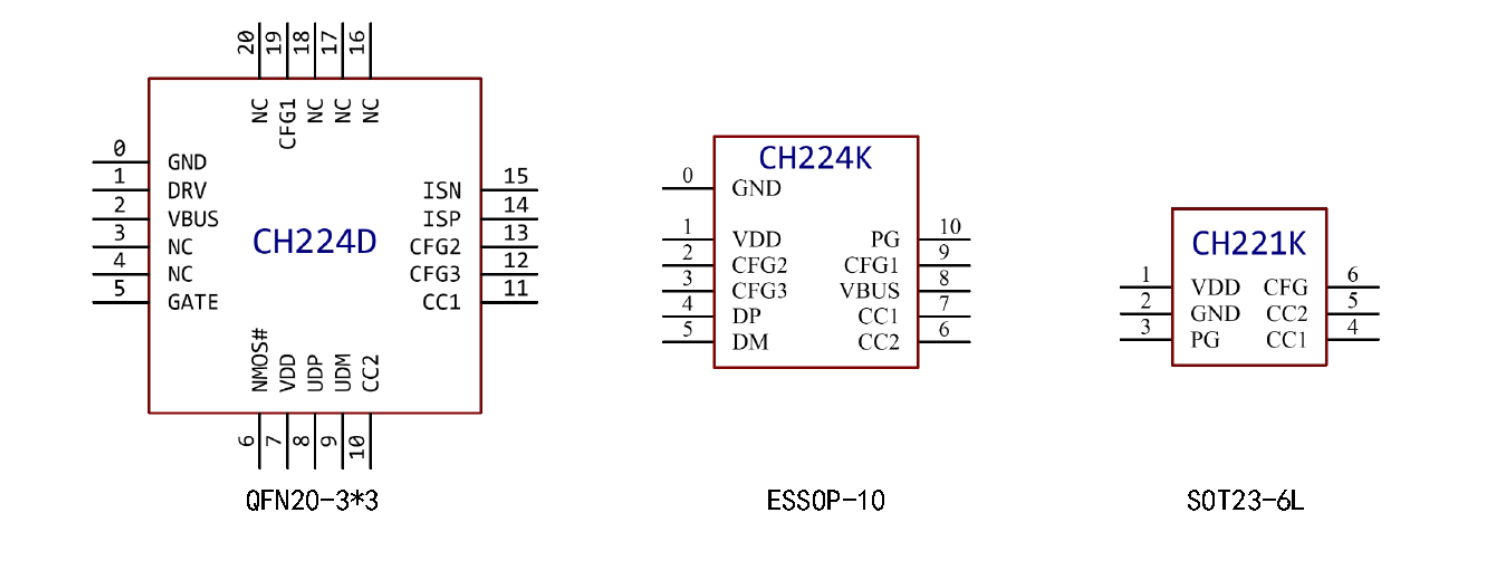

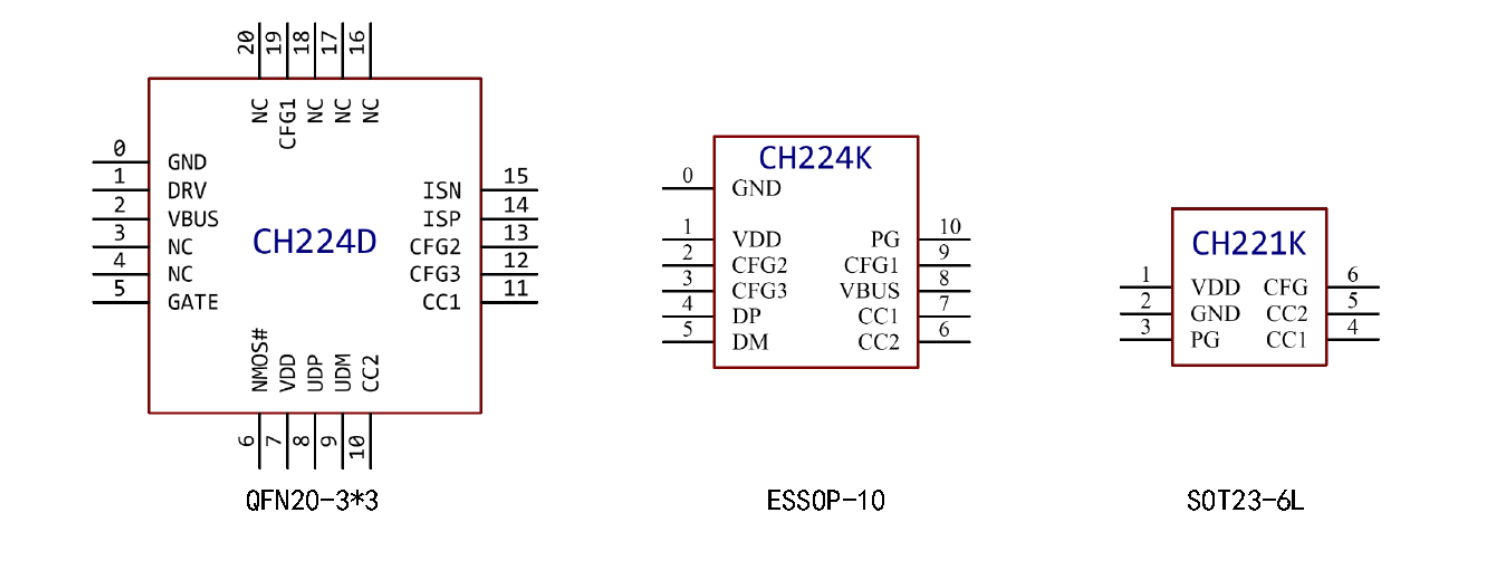

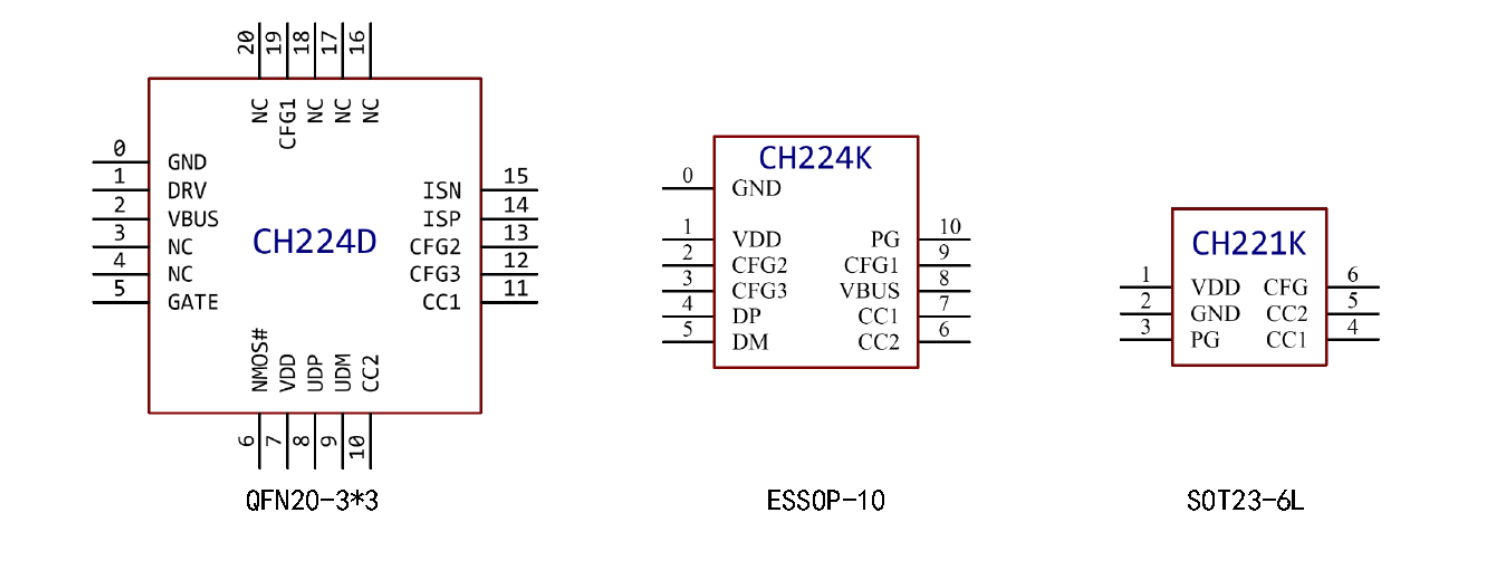

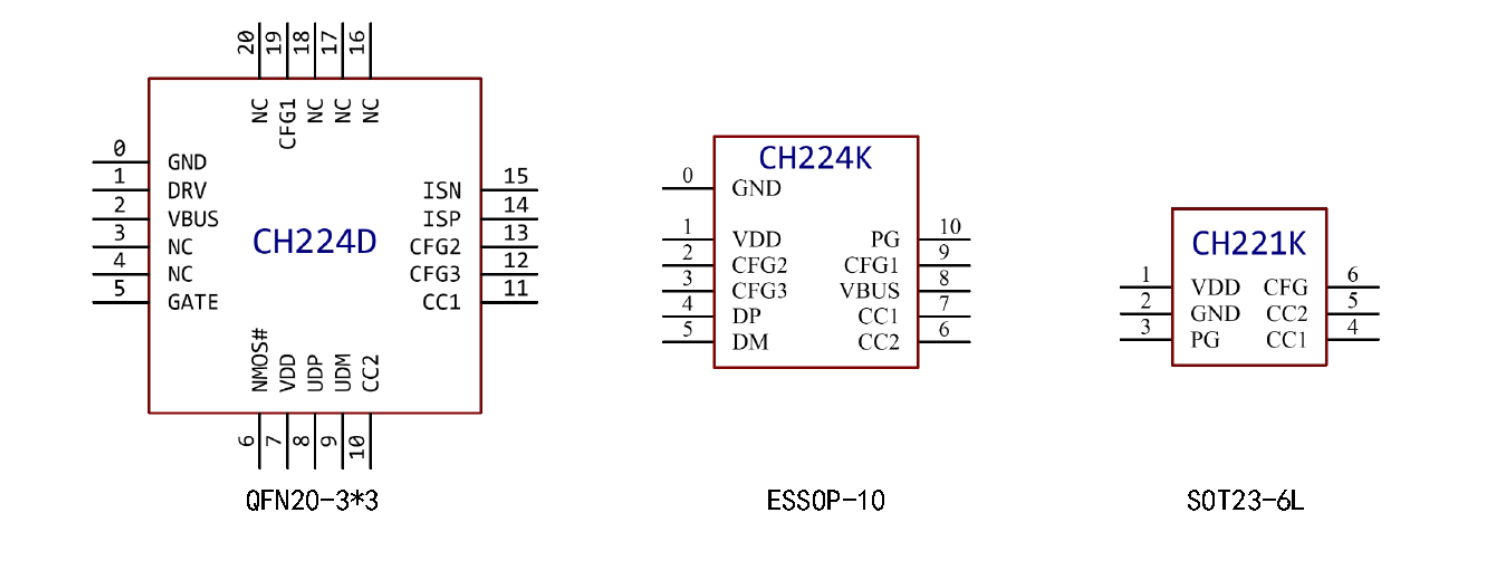

| 引脚号 | 引脚名称 | 类型 | 引脚说明 |

|---|---|---|---|

| 0 | GND | 电源 | 公共接地端,散热底板 |

| 1 | VDD | 电源 | 工作电源输入,外接 1uF 退耦电容,串联电阻至 VBUS |

| 4,5 | DP,DM | 双向 | USB 总线 |

| 6,7 | CC1,CC2 | 双向 | Type-C CC 总线 |

| 2,3,9 | CFG1,CFG2, CFG3 | 模拟输入 | 电源档位配置输入 |

| 8 | VBUS | 模拟输入 | 电压检测输入,需要串联电阻至外部输入 VBUS |

| 10 | PG | 开漏输出 | 默认 Power Good 指示,低电平有效,可定制功能 |

功能描述

概述

CH224是一款支持PD3.0/2.0,BC1.2等升压快充协议输入的协议电源受电端IC,支持4~22V范围内电 压的请求,并可通过多种方式动态配置优先请求的电压档位。

CH224K提供单电阻配置方式和电平配置方式。

CH224K电压档位配置

单电阻配置:

适用于同一 PCB 通过修改电阻阻值实现不同请求电压的应用场合。 CFG1对GND连接电阻,不同阻值对应不同的电压请求档位。

使用单电阻配置方式时,CFG2和CFG3引脚 可悬空。电阻-请求电压对照表如下。

| CFG1上阻值 | 请求电压 |

|---|---|

| 6.8KΩ | 9V |

| 24KΩ | 12V |

| 56KΩ | 15V |

| NC | 15V |

电平配置:

适用于 MCU 动态调整请求电压,或 PCB 线路固定请求电压的应用场合。

CFG1,CFG2,CFG3直接连接到外部MCU的IO口,或直接连接CH224K/CH224D芯片的VDD/GND管脚,使用 电平对请求电压进行配置。真值表如下。

| CFG1 | CFG2 | CFG3 | 请求电压 |

|---|---|---|---|

| 1 | - | - | 5V |

| 0 | 0 | 0 | 9V |

| 0 | 0 | 1 | 12V |

| 0 | 1 | 1 | 15V |

| 0 | 1 | 0 | 20V |

使用电平配置方式时,需注意使用的 IO 口电压和默认状态。 对于 CH224K 来说,CFG2/CFG3 引脚输入电压不可高于 3.7V。

若 MCU 等后端电路启动较慢,或 MCU 管脚有特定的默认状态,启动前 CFG1 将可能会处于浮空状态或 IO 配置模式,此时则有可能请求 20V,若系统无法承受 20V 输入,则应当在 CFG1 引脚添加配置电阻,以 保证 MCU 启动前,CH224K 可以通过电阻配置,请求合适的电压。

参考原理图

1.CH224K使用 Type-C 母口,单电阻配置 9/12/15/20V(图中电阻配置 6.8KΩ 为 9v)

2.CH224K 使用 Type-C 母口,电平配置 5/9/12/15/20V(图中电平方式配置为 12v)

2.CH224K 使用 Type-C 母口,电平配置 5/9/12/15/20V(图中电平方式配置为 12v)

3.CH224K 使用 Type-C 公口,仅使用 PD 协议和 E-Mark 模拟功能(图中电阻配置 NC 为 20v)

3.CH224K 使用 Type-C 公口,仅使用 PD 协议和 E-Mark 模拟功能(图中电阻配置 NC 为 20v)

参数

CH224K 芯片绝对最大值

| 名称 | 参数说明 | 最小值 | 最大值 | 单位 |

|---|---|---|---|---|

| TA | 工作时的环境温度 | -40 | 100 | ℃ |

| TS | 储存时的环境温度 | -55 | 125 | ℃ |

| VDD | 工作电源电压(VDD 引脚接电源,GND 引脚接地) | -0.5 | 6 | V |

| VIOHV | VBUS 引脚上的电压 | -0.5 | 24 | V |

| VIOCC | CC1,CC2 引脚上的电压 | -0.5 | 20 | V |

| VIOUX | DP,DM,CFG1,CFG2,CFG3,DRV,NMOS#,ISP,ISN 引脚上的电压 | -0.5 | VDD+0.5 | V |

| VIOHX | GATE 引脚上的电压 | -0.5 | VIOHV+6.5 | V |

| PD | 整个芯片的最大功耗(VDD 电压*电流) | 300 | mW |

封装信息

| 封装形式 | 塑体宽度 | 引脚间距 | 封装说明 |

|---|---|---|---|

| ESSOP10 | 3.9mm | 150mil | 1.00mm |